MISO:主裝置資料輸出,從裝置資料輸入MOSI:主裝置資料輸入,從裝置資料輸出SCLK:時鐘訊號,由主裝置產生CSn:從裝置使能訊號,由主裝置控制,低電平有效2.1 SPI 讀寫注意事項SPI介面上的所有傳送都是以一個頭位元組(heade

/*程式 OV7670驅動程式作者:兔子效果:驅動攝像頭OV7670帶FIFO模組,拍攝1幀圖片,並將圖片資料透過串列埠上傳至電腦時間:19

如果當前請求訊號是A,那麼之後輪詢的是BCA,如果當前請求訊號是B,那麼之後輪詢的是CAB,如果當前請求訊號是C,那麼之後輪詢的是ABC狀態機實現6.IIC協議(FPGA實戰)學習第二階段:System Verilog學習學習計劃前期學習以

整體的設計框架如下:埠定義如下:埠名方向描述ClkInput主時鐘,預設頻率為50MHzRst_nInput復位訊號,低有效RsRxInput串列埠接收埠RSTxOutput串列埠傳送埠Tx_data_in[7:0]Inputtx端要發

經過一些查詢資料後:解題思路:假設:寫時鐘頻率 w_clk, 讀時鐘頻率 r_clk, 寫時鐘週期裡,每B個時鐘週期會有A個數據寫入FIFO 讀時鐘週期裡,每Y個時鐘週期會有X個數據讀出FIFO 則,FIFO的最小深度計算公式如下: fi

2 重要引數FIFO中重要的引數有深度、寬度、空標誌、滿標誌、讀時鐘、讀時針、寫時鐘和寫時針我看到過一個很形象的比喻:把FIFO比作汽車進入一個單向行駛的隧道,隧道兩端都有一個門進行控制,FIFO寬度就是這個隧道單向有幾個車道,FIFO的深

已經有資料的儲存單元個數為下一個寫地址減去讀地址格雷碼的寫同步的二進位制碼,當其大於儲存單元數-1時,產生組合邏輯的幾乎滿訊號,在寫時鐘下產生時序邏輯的幾乎滿訊號

對ram進行寫入和讀出控制,這裡用到了for迴圈去控制寫,當寫使能有效的時候,並且寫地址為迴圈數i時,將寫資料寫入mem[i]

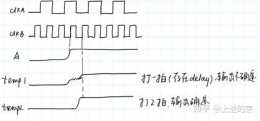

n亞穩態的產生以及對設計的可靠性的影響n 透過相位控制避免亞穩態n 在時鐘域之間傳輸單個訊號,將訊號打兩拍n 使用FIFO在時鐘域之間傳輸多位資料n 使用分割槽同步器模組提高設計的組織架構l 處理ASIC驗證原型裡的門控時鐘n 建立一個單時

7、格雷碼我們知道了,讀地址需要跟寫地址比較來產生空和滿訊號,然後對於非同步FIFO,讀寫為不同時鐘,如果直接取樣,就會有:類似前面資料產生多位亞穩態的問題,比如寫地址從00111改變從01000的時候,讀時鐘恰好取樣,那麼除了最高位外,其

所以我建議專家們再寫這種FPGA入門書籍,就講非同步FIFO,內容能說很多,而且覆蓋面還真挺廣的,實現階段,還可以看這種跨時鐘佈線工具報的警告,基本上需要的概念都能cover掉了

設計程式碼為:module uart_drive (input wire clk,input wire rst_n,input wire tx_clk,input

//write data to fifo buffer and wr_pointer controlalways@(posedge wr_clk) beginif(wr_rst) beginwr_pointer <= 0

關於非同步處理,以下說法正確的是:A、靜態配置訊號可以不做非同步處理B、非同步FIFO採用格雷碼的原因是為了提高電路速度C、非同步處理需要考慮傳送和接收時鐘之間的頻率關係D、單位元訊號打兩拍後可以避免亞穩態的發生答案:AC解析:A

U//cnt++hanning_signal

本篇介紹的 非同步FIFO 設計原理是基於上一篇文章推薦的論文《Simulation and Synthesis Techniques for Asynchronous FIFO Design》,我將會從以下幾點來總結:FIFO整體架構及模

(3)專案中遇到的難點(4)FIFO空滿訊號產生的三種方法(5)畫出格雷碼跨時鐘域的電路圖(6)智力題:時分鐘指標的追擊重合問題【瑞晟微】- 面試問題 -(1)慢時鐘採快時鐘怎麼處理

實現簡單效能較差,調出的頁面可能是經常訪問的Belady現象:程序分配物理頁面數增加時,缺頁並不一定減少,例子(記憶體中能裝4頁,但實際有5頁,最優演算法為2次):很少單獨使用6