基於UART的序列資料傳輸不需要使用時鐘訊號來同步傳輸的傳送端和接收端,而是依賴於傳送裝置和接收裝置之間預定義的配置

STM32F4系列MCU時鐘模式該時鐘源是由外部無源晶體與MCU內部時鐘驅動電路共同配合形成,有一定的啟動時間,精度也較高,但是一定要正確使用

判斷晶振效能優良還需要結合頻率誤差、溫度穩定性、起振時間、相位噪聲與抖動等引數

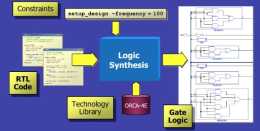

大概是這樣的:總體來說,分為以下幾個基本步驟:Floorplan階段Floorplan 階段主要是對整個設計進行一個宏觀的規劃(由於面向初學者,故這裡所說的都是block級別,後續會慢慢帶領大家列出頂層相關的設計)這裡的宏觀規劃包括像模組大

1 檢查當前時區檢查當前時區用到的命令其實在上文中已經提到過,為timedatectl,當該命令不帶任何引數時可以檢視時區和時間,如下顯示的時區為Asia/Shanghai[root@hadoopmaster ~]# timedatectl

此外快取設計中用於判斷tag是否命中等的邏輯是關鍵路徑,訪問ram加上判斷tag等邏輯往往無法在一個時鐘週期下完成,所以一般需要構成數字流水線,分幾拍得到命中結果,加之很多額外的hazard判斷來操作流水線

如果時鐘結構比較複雜,建議編寫CTS constraint,來引導工具build tree定義好stop pin ignore pin exclude pin floating pin等哪些clock是需要做inter-balance的衡量

瓦林,他的兩個女兒瑪格麗(Margaret)和簡(Jane),以及他的兩個幫工約翰·阿徹(John Archer)和約翰·雷恩(John Leyns)都死於非常致命的第二次瘟疫侵襲,瘟疫發生在黑修士(Blackfriars)的聖安妮教區及

支援黑色和白色主題切換、透明度設定、設定為桌面動態時鐘和螢幕保護程式、支援自定義字型、秒針選項

分析抖動以及其具體產生原因將有助於在系統設計時儘可能的減少抖動產生的影響,並保證系統 BER 低於某個最大值,同時可以確定抖動對 BER 的影響,並保證系統 BER 低於某個最大值,通常是10^-12抖動的形成原因直觀的表示如下圖:圖 抖動

圖 5 產生的 ADC SNR 受熱噪聲和時鐘抖動的限制圖 6 每十倍頻計算得到的時鐘相位噪聲抖動影響確定正確的整合下限在取樣過程中,輸入訊號與取樣時鐘訊號混頻在一起,包括其相位噪聲

Problem 83 : DFF with reset value (Dff8p)牛刀小試與上題的不同點在於,復位後的值不再是 0 (那麼即為 1,對於 1bit 來說也沒別的選擇了),另外觸發器的觸發事件從時鐘上升沿變成了時鐘下降沿,這些

以下verilog程式碼中,clk,rst_n分別為時鐘和復位訊號,敘述不正確的有:input clk, rst_n

想要了解的小夥伴,可直接在App Store搜尋氫時鐘,就可以了

你轉90度,地鐵向前走,再轉,向右,再轉,向後亂轉,向某個角度走不就是觀察角度和參考系不同導致對運動狀態的描述有差異麼跟空間有毛線關係因為法向量方向不一樣,你可以把你的視角看成是法向量

4、Clock Arrival Time: 目的暫存器時鐘到達時間 5、Data Required Time --- Set up:建立時間的資料需求時間: 6、Data Required Time – Hold:保持時間的資料需求時間:

貓眼專業版一款為電影行業從業者提供及時、準確、專業的電影票房資料分析的軟體(秒級實時票房,排片,影院經營資料等)它能為影視從業者提供資訊互通平臺,提高影視作品製作效率(劇組成員招募,行業精英對接,找劇組、投資、導演、演員、攝影等)

關鍵屬性.HashedWheelTimeout next,prev:當前定時任務在連結串列中的前驅和後繼引用TimerTask task:實際被排程的任務long deadline:該時間是相對於引擎的startTime的,由公式curre

if-else裡面有if就要有對應的else),否則綜合時會推匯出LATCH(而不是你想要的組合邏輯),影響功能,而RTL模擬時case寫得不完整多半是不影響功能的

0 BCSCTL1(Basic Clock System Control 1)暫存器,地址58H,初始值84HXT2OFF:控制XT2振盪器的啟停,0為開啟,1為關閉XTS:選擇LFXT1工作在低頻晶體模式(XTS=0)還是高頻晶體模式(X