STA分析與建模-CH3 基本時序模型簡介

基本時序模型簡介

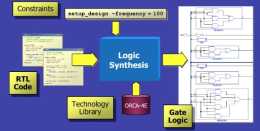

快速時序模型(Quick Time Model):一般在設計早期對模組的設計時序進行預估,透過時序資訊庫對應單元的時序弧資訊,把需要建模的時序路徑的時序弧近似為某些單元的時序弧組合(直接累加).

如圖3-1所示模組中:

,

其他延時計算方法類似,建模後包含資訊如圖3-2所示。

2。

介面邏輯模型(Interface Logic Model): 將原始電路簡化為只包含介面邏輯的一個小電路,不浩瀚內部觸發器到觸發器的路徑邏輯資訊。

3. 抽取時序模型(Extracted Timing Model): 從模組的門級網表裡抽取了時序資訊,隱藏單元內部的實現細節.

4. Stamp模型:由PT生成,已過時.

5. Synopsys工藝庫模型:每個standard cell都需要一個標準時序模型,標準單元效能引數文件如圖3-7所示,為目前的業界標準時序模型,.lib檔案中即為該種模型,包含對一個單元功能,時序以及一些其他引數如面積、功耗和設計規則的描述,下文重點介紹Synopsys工藝庫模型。

Synopsys工藝庫模型

目前大部分時序庫均採用Synopsys標準建模語言進行描述,目前常用的Synopsys工藝庫分為以下三種:

1.

線性延時模型(Linear Delay Model)

該模型定義單元的門延時 和輸出端轉換延時(Transition time) 是

基於

輸入埠轉換延時

和輸出負載這兩個變數的線性方程式

來表達的。但實際情況中,門延時與輸入訊號跳變時間與輸出負載間不是遵循嚴格的線性關係,精度有限。

2. 非線性延時模型(Non-linear Delay Model)

能精準表達出輸入端和輸出端的延時。由驅動模型和接收模型組成,驅動模型為戴維南(Thevenin)等效電壓源,接收模型為單一制定的接收端電容負載。由於在。13工藝及以上,互連線電阻遠小於驅動電阻,在這些工藝下該模型有效。

3. 複合電流源延時模型(Composite Current Source Delay Model, CCS延時模型)

在。13工藝以下,

互連線電阻開始超過邏輯閘的電阻大小,成為決定時序延時的主要影響因素

。且由於在先進工藝下,由於電晶體中增大的米勒效應(Miller Effect),其邏輯閘輸出波形不再像以前一樣保持線性,邏輯閘輸出波形的非線性導致前面介紹的非線性延時模型無法滿足對邏輯閘的輸出波形進行精確建模。因此在先進工藝下,採用CCS模型劍魔更精確,其也是

由驅動模型和接收模型組成

的,如圖3-10所示。

CCS模型的驅動模型是一個基於時間和電壓的非線性電流源,同時設定電流源的驅動電阻為無窮大,因此即使邏輯閘的驅動電阻遠低於互連線電阻,該模型仍然能夠提供很高的計算精確度。同時該模型達到高精度的另一個方面是

不透過對電晶體的行為進行建模,而是對隨機情況下電晶體在不同的集總負載下的行為進行取樣

。透過對應不同的輸入轉換狀態和輸出負載狀態,複合電流源延時模型

儲存了電流數值

,進而推匯出邏輯閘的輸出引腳響應。

複合電流源延時模型的資訊提取方法與非線性延時模型類似: 指定輸入訊號轉換時間和邏輯閘的輸出端負載值,

透過電路模擬模擬出邏輯閘的延時和輸出轉換時間

。但是複合電流源延時模型

提取的是輸入埠的電流值和輸出負載的電流值

, 同時

輸入埠的電流值用於構成接收模型資料

,

輸出負載的電流值用於構成驅動模型資料

。提取模型時,給Cell加上不同Transition time的輸入訊號和不同負載電容的組合,採集輸入輸出節點的電流建模。

延時計算模型

目前常用的延時計算模型主要分為以下兩種

CMOS通用延時計算模型

該模型將時序路徑的延時分為4部分,總延時為四部分之和。其中DI為邏輯閘

固有的本徵延時

,DS為

輸入訊號轉換延時

,DC為

訊號連線延時

,DT為

輸出訊號轉換延時

,具體計算方法在書P38-39。訊號互連線延時可由三種不同的互連線計算模型來計算:

best_case_tree, worst_case_tree, and balanced_tree

, 三種方法的區別在於 對互連線總電阻電容負載 的不同處理方法。

2。

CMOS非線性延時計算模型 (NLDM)

NLDM模型計算精度較高,為目前業界主要採用的模型,該延時模型

由輸入訊號轉換時間與輸出負載作為索引,時序分析時以一個二維查詢表的形式來計算延時

,查詢表的實際構成如下圖所示。在計算時透過索引到對應的取樣點,再透過

插值法

來計算延時。

具體方法為設計算點的輸入埠Transition time為X,輸出負載電容為Y,延時為Z,則延時Z可以表達為

,

再透過取計算點附近的四個取樣點,即可帶入方程中即可解出A, B, C, D的值,進而計算出計算點延時Z的大小。

透過這種方法計算的總延時由兩部分構成

.

其中

為訊號互連線延時,計算方法可由之前提到的互連線計算模型方法來計算。

為邏輯閘轉換延時,。lib檔案中對應的查詢表為rise_transition與fall_transition。

為邏輯閘傳播延時,為輸入訊號50%到輸出訊號10%(上升沿)或90%(下降沿)的延時,。lib檔案中對應的查詢表為rise_propagation與fall_propagation。

為邏輯閘延時,為輸入50%到輸出50%的延時,查詢表為cell_rise和cell_fall。

的計算,可透過直接對輸入transition time和輸出負載進行索引插值,得到

。也可以對輸入

和輸出負載進行索引插值得到

,再與

相加得到

。在計算完成後,同樣

需要考慮PVT帶來的變化

,故最後都需要乘以一個比例係數。

互連線計算模型(3.4)

輸出訊號透過訊號線傳播到下一級邏輯閘輸入端的時間為訊號互連線傳播延時。晶片內部的互連線可大致分為三種:

短線:用於門之間的連線,長度遠小於訊號波長,主要受寄生電容和耦合電容的影響;

中長線:即模組間互連線,電感耦合效應變得更突出;

長線:即全域性互連線,如電源線等,長線,即全域性互連線。長線對電路效能起著關鍵作用。長線特別需要採用低電阻率金屬以減小訊號線和電源線的電阻損耗,需要厚的絕緣層來增加特徵阻抗、減小延時,需要較寬的線間距減小串擾

1. 互連線計算模型

a. 集總C模型

導線電阻小,頻率低時可使用,只考慮導線的電容部分,並把分佈的電容集總為單個電容,在先進工藝下精度低。

b. 集總RC模型

導線長度超過幾個微米後會有明顯的電容,故採用RC模型,如圖3-27所示,集總模型中大多數模型可標識為3-28中所示的RC樹,可用Elmore延時計算RC樹的延時,圖中延時即為,具體計算方法Rabeay書中有講。Elmore模型非常簡單,演算法僅為乘加,但不能處理電感,且其悲觀估計了延時,精度不高。

c. 分佈RC模型

是比較常用的模型,主要為L模型,π模型,T模型,Rabeay書中有細講,這裡不再贅述。

d. 傳輸線模型

加入了電感因素,但計算量太大。

2. 線負載時序模型

使用RTL程式碼在綜合階段做STA時,使用線負載模型來估算實際物理實現後的線負載大小,線負載模型在時序資訊檔案中的內容如下:

#取自UMC55 TC 。lib庫

wire_load

(

“wl0”

)

{

resistance

:

0

;

capacitance

:

0。000171

;

area

:

0

;

slope

:

1

;

fanout_length

(

1

,

1

);

}

wire_load

(

“wl10”

)

{

resistance

:

0。002464

;

capacitance

:

0。000171

;

area

:

0。09

;

slope

:

21。7

;

fanout_length

(

1

,

21。7

);

}

wire_load

(

“wl20”

)

{

resistance

:

0。002464

;

capacitance

:

0。000171

;

area

:

0。09

;

slope

:

43。4

;

fanout_length

(

1

,

43。4

);

}

引數

resistance

定義互連線單位電阻值,引數

capacitance

定義互連線單位電容值,引數

area

定義互連線單位長度的面積值,引數

slope

定義擴充套件斜率值,引數

fanout_length

定義對應扇出大小的互連線長度。各個屬性均可由 互連線長度×各個引數得到。

引腳電容值的計算(3.5)

時序模型中還包含了輸入引腳的電容資訊,如下所示,電容值可由

流入輸入引腳電流的積分,或基於輸出轉換時間透過查詢表確定對應輸出電容負載

pin

(

A

)

{

capacitance

:

0。00238681

;

direction

:

input

;

fall_capacitance

:

0。00237906

;

fall_capacitance_range

(

0。00206518

,

0。00249992

);

input_voltage

:

default

;

max_transition

:

0。63

;

related_ground_pin

:

VSS

;

related_power_pin

:

VDD

;

rise_capacitance

:

0。00239456

;

rise_capacitance_range

(

0。00207666

,

0。00250963

);

}

功耗模型的計算(3.6)

功耗計算包括開關功耗Isw,短路電流功耗ISC,亞閾值漏電流功耗Ilk。 動態功耗由開關功耗與短路功耗組成,漏電功耗則為靜態功耗。功耗資訊查詢表的結構如下所示,查詢的引數為transition time

internal_power

()

{

related_pg_pin

:

“VDD”

;

related_pin

:

“C”

;

when

:

“A&!B&!D&ICI”

;

fall_power

(

pwr_tin_oload_7x7

)

{

index_1

(

“0。002, 0。0132966, 0。0529503, 0。128675, 0。246649, \

0。412182, 0。63”

);

index_2

(

“0。001, 0。00203855, 0。00568408, 0。0126457, \

0。0234917, 0。0387098, 0。0587347”

);

values

(

“0。00728954, 0。00725657, 0。00721903, 0。00721103, 0。00720768, 0。00720472, 0。00720381”

,

\

“0。00729078, 0。0072634, 0。00721792, 0。0072154, 0。00720773, 0。00720936, 0。00720859”

,

\

“0。007291, 0。00725405, 0。0072229, 0。00720875, 0。00720669, 0。00720287, 0。00720341”

,

\

“0。00732656, 0。00728652, 0。00723918, 0。00722715, 0。00722151, 0。00721831, 0。00721746”

,

\

“0。0074923, 0。00742634, 0。00734396, 0。00731135, 0。00729386, 0。00728777, 0。00728414”

,

\

“0。007753, 0。00766063, 0。00752834, 0。00746298, 0。00743617, 0。00742397, 0。00741453”

,

\

“0。00811118, 0。00799418, 0。00780421, 0。00771007, 0。00766039, 0。00763781, 0。00762595”

);

}

rise_power

(

pwr_tin_oload_7x7

)

{

index_1

(

“0。002, 0。0132966, 0。0529503, 0。128675, 0。246649, \

0。412182, 0。63”

);

index_2

(

“0。001, 0。00203855, 0。00568408, 0。0126457, \

0。0234917, 0。0387098, 0。0587347”

);

values

(

“0。0057168, 0。00570606, 0。00569397, 0。00569374, 0。00569302, 0。00569989, 0。00570323”

,

\

“0。00571685, 0。00570193, 0。00569029, 0。0056922, 0。00569131, 0。00569866, 0。0057019”

,

\

“0。00571847, 0。00570009, 0。00568423, 0。00568814, 0。00568003, 0。00569252, 0。00569621”

,

\

“0。00577125, 0。00574691, 0。00569955, 0。00569777, 0。00569011, 0。00569759, 0。00570075”

,

\

“0。00590104, 0。00586591, 0。00580413, 0。00576284, 0。00575733, 0。00575026, 0。00575951”

,

\

“0。00611359, 0。00606702, 0。00596568, 0。00591046, 0。00587301, 0。00586805, 0。00586793”

,

\

“0。00643876, 0。00635698, 0。00620943, 0。00613788, 0。00608604, 0。00606304, 0。00605462”

);

}

}

時序資訊建模基本方法

(3.7)

時序模型通常考慮兩方面延時資訊,一個是輸入到輸出的延時資訊,即

時序弧,

一個是輸入埠存在的時序約束資訊,比如建立或保持時間約束,即

約束時序弧

。

當模組規模較大時可對時序弧進行化簡,有兩種花間方式:時序弧串聯合並和時序弧並聯合併。

上一篇:長春婚紗照哪家好婚紗照前十名

下一篇:平面設計作品缺少設計感怎麼辦?